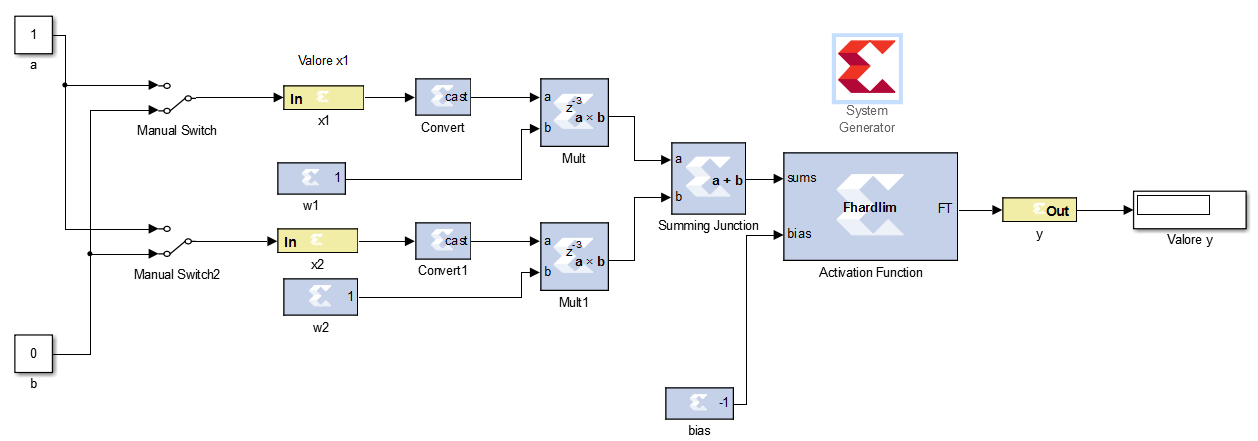

In questo articolo per la rivista Elettronica Open Source avevamo già visto sia la teoria sia la pratica su come realizzare un modello con Simulink (Matlab) e System Generator di una semplice rete neurale artificiale (ANN) perceptron e come eseguirne l’addestramento con NNTOOL. Seguendo un procedimento analogo possiamo implementare il nostro perceptron su un FPGA.

Tech Stack

[1] Vivado 2017.3

[2] Matlab R2017a

[3] System Generator 2017.3

Perceptron

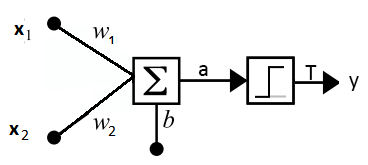

Vogliamo realizzare un semplice perceptron a due ingressi x1,x2

La prima parte della rete calcola il potenziale di attivazione a

n∑i=1wixi=w1x1+w2x2−θ>0

La seconda parte, invece, serve a calcolare il valore del segnale di uscita y

y=T(n∑i=1wixi=w1x1+w2x2−θ>0)

Hardlim

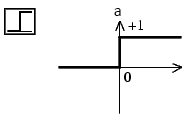

La funzione di trasferimento T

y=T(a)={1a≥00a<0

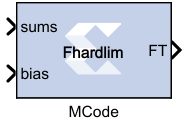

System Generator include il blocco M-Code che può essere utilizzato per scrivere il codice Matlab per la funzione di trasferimento.

function [FT] = Fhardlim (sums,bias)

activation= sums + bias;

if activation >= 0

ft1 = 1;

else

ft1 = 0;

end

FT=ft1;

L’immagine seguente mostra com’è il blocco dopo che il modello è stato compilato:

– due ingressi (sums, bias)

– una sola uscita (FT).

System generator

Simulink è un ambiente grafico per il Model-Based design che supporta la progettazione , la simulazione, la generazione automatica del codice, il testing e la verifica di sistemi embedded.

System Generator (SysGen) è un toolbox per la modellazione hardware fornito da Xilinx integrato con ISE Design Suite o Vivado HLx che consente di lavorare in ambiente Simulink attraverso un block-set con più di 80 funzioni.

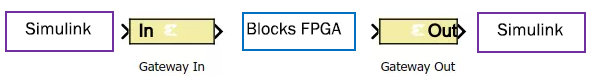

I blocchi di SysGen non convertono automaticamente i numeri a virgola mobile (floating point) di Simulink in virgola fissa (fixed point). Infatti dobbiamo utilizzare i blocchi Gateway In e Gateway Out per convertire da floating point a fixed point e viceversa.

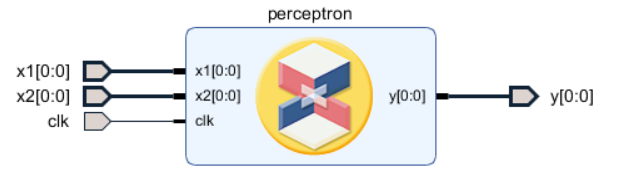

I nomi che associamo ai gateways in input e output corrisponderanno a quelli della entity del codice VHDL generato da SysGen. Quindi avremo i due inputs x1,x2

Addestriamo la rete neurale

In Prontuario filo-logico per un elettronico avevamo già visto come il connettivo OR risulta falso solo se entrambi i valori sono falsi (0+0=0), vera se almeno uno dei due valori è vero (1+0=1;0+1=1;1+1=1).

Dalla Command Window di Matlab dichiariamo i valori della nostra tavola di verità come una matrice in entrata (inputs) e in uscita (target) con i valori che la rete dovrà apprendere.

>> inputs = [0 0 1 1;0 1 0 1]; >> target = [ 0 1 1 1];

Ora dobbiamo inizializzare l’oggetto perceptron indicando che abbiamo come valori minimi e massimi di addestramento i due inputs con un range [0 1] e che la nostra rete è composta da un solo neurone.

>> perceptron = newp([0 1; 0 1],1);

Ogni ciclo di apprendimento della rete neurale viene detto epoca (epoch) e dobbiamo indicarne un numero sufficiente perché la nostra rete possa apprendere correttamente. Addestriamo il perceptron ad esempio per 10 epoche anche se di solito ne impiega solo 3 essendo una rete molto semplice.

>> perceptron.trainParam.epochs = 10; >> perceptron = train(perceptron,inputs,target);

Di default i pesi sinaptici (weights) e bias hanno un valore iniziale di 0

>> perceptron.IW{1} %weights

ans =

1 1

Non ci resta che inserire i valori ottenuti nei corrispettivi constant blocks di SysGen

>> net.b{1} %bias

ans =

-1

System Generator Token

Il token System Generator è un blocco speciale della libreria Xilinx Blockset che

contiene le informazioni indispensabili per trasformare il nostro modello in Simulink in VHDL.

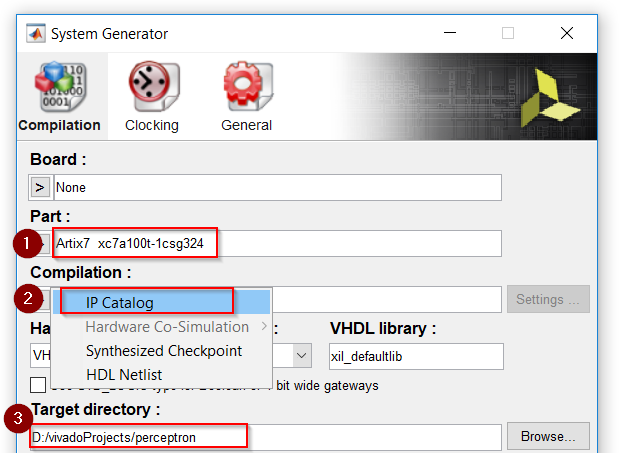

Dal modello facciamo doppio click nel token di System Generator e selezioniamo la scheda FPGA (1) a nostra dispozione e il tipo di compilazione (2) desiderata.

Dal modello facciamo doppio click nel token di System Generator e selezioniamo la scheda FPGA (1) a nostra dispozione e il tipo di compilazione (2) desiderata.

Infine selezioniamo la cartella di destinazione (3) di dove verranno generati i files.

Una volta clickato il pulsante Generate vengono aperte le finestre di stato di compilazione che indicano l’avanzamento del flusso per la generazione dei files VHDL.

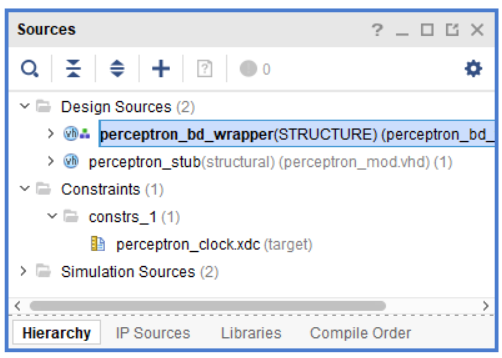

Perceptron: IP-Core

Un progetto Vivado è organizzato in blocchi IP (Intellectual Property) di cui quello inserito per primo è il Top Module.

Con SysGen possiamo realizzare un modulo IP-Core del perceptron che possiamo ritrovare nel catalogo IP-Core di Vivado.

Con SysGen possiamo realizzare un modulo IP-Core del perceptron che possiamo ritrovare nel catalogo IP-Core di Vivado.

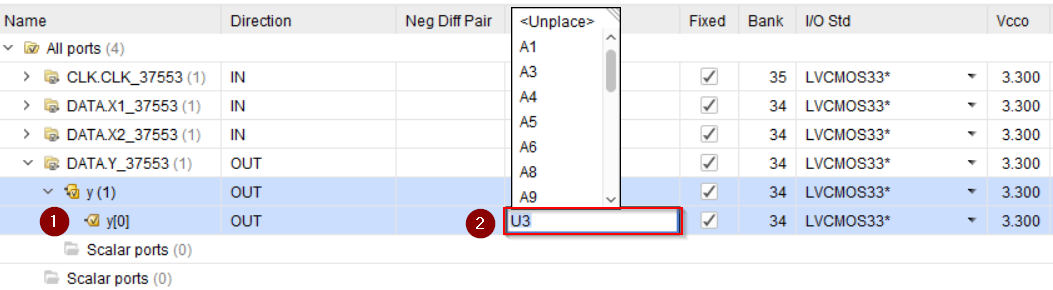

I tools per la descrizione hardware di Xilinx utilizzano due tipi di files diversi per la location dei IO pins: UCF (user contraits files) e XDC (xilinx design contraints). Usati rispettivamente da ISE e Vivado.

Ora da Resource Center scarichiamo dalla sezione Design Resources il design contraints per il Nexys4, associando ad esempio il led (U3

Possiamo impostare il file XDC in due modi:

Creando il file .xdc manualmente

create_clock -period 20.000 -name clk [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports {x1[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {x2[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {y[0]}]

set_property PACKAGE_PIN U3 [get_ports {y[0]}]

set_property PACKAGE_PIN E3 [get_ports clk]

set_property PACKAGE_PIN U4 [get_ports {x1[0]}]

set_property PACKAGE_PIN V2 [get_ports {x2[0]}]

Oppure utilizzando la GUI di Vivado

Dobbiamo ricordarci di selezionare I/O Standard LVCMOS33 è un standard CMOS a bassa tensione che usa la tensione di alimentazione di 3.3V.

Dobbiamo ricordarci di selezionare I/O Standard LVCMOS33 è un standard CMOS a bassa tensione che usa la tensione di alimentazione di 3.3V.

Bibliografia

[1] Donald O. Hebb, L’organizzazione del comportamento: una teoria neuropsicologica, Franco Angeli, 1975

[2] David Rumelhart,James McClennand, Parallel Distributed Processing, 1986

[3] Silvio Cammarata, Reti neuronali, dal perceptron alle reti caotiche e neuro-fuzzy,1997

[4] James A. Anderson, Edward Rosenfeld, Talking Nets, An oral History of Neural Networks, Mit, 2000

Nexys

[1] Nexys 4, Digilent

[2] Nexys 4 Reference Manual, Digilent

Vivado

[1] Vivado Design Suite:Model-Based DSP Design Using System Generator, Xilinx,UG948, 2016

[2] Sanjay Churiwala, Designing with Xilinx FPGAs: Using Vivado, Springer, Springer, 2016

JEDEC Standard

[1] Interface Standard for Nominal 3 V/3.3 V Supply Digital Integrated Circuits, JESD8C.01, 2007

Model-based design

[1] Ali Behboodian, Model-based design: a Methodology that adresses today’s growing challenges of designing embedded systems, DSP Magazine,2006